# Detector Developments for the LHC: CMS TOB Silicon Detector Modules and ATLAS TileCal Read-Out Driver

# Departament de Física Atòmica, Molecular i Nuclear Universitat de València

April 29th, 2005

Directors: Juan A. Valls Ferrer Antonio Ferrer Soria En ANTONIO FERRER SORIA, Catedràtic de la Universitat de València y membre del Departament de Física Atòmica, Molecular i Nuclear de la Facultat de Física de la Universitat de València i de l'Institut de Física Corpuscular (IFIC) de València.

CERTIFICA:

Que la present memòria "Detector Developments for the LHC: CMS TOB Silicon Detector Modules and ATLAS TileCal Read-Out Driver" ha sigut realitzada sota la meva direcció i la del Dr. JUAN ANTONIO VALLS FERRER en el Institut de Física Corpuscular (Centre Mixt Universitat de València – C.S.I.C.) per En JOAQUÍN POVEDA TORRES y constitueix el seu treball d'Investigació per a optar al Diploma d'Estudis Avançats (D.E.A)

I per a que conste, en compliment de la legislació vigent, firmem el present Certificat a 12 d'Abril de 2004.

Dr. Antonio Ferrer Soria

Dr. Juan Antonio Valls Ferrer

# Index

| L  | LAYOUT                                                                   | 15 |

|----|--------------------------------------------------------------------------|----|

| // | INTRODUCTION                                                             | 17 |

| 1  | CERN                                                                     |    |

| 2  | 2 THE LARGE HADRON COLLIDER (LHC)                                        | 20 |

| 3  | 3 EXPERIMENTS FOR THE LHC                                                |    |

|    | 3.1 GENERAL STRUCTURE FOR PARTICLE PHYSICS EXPERIMENTS                   | 22 |

|    | 3.2 COMPACT MUON SOLENOID (CMS)                                          |    |

|    | 3.2.1 Inner Detector                                                     |    |

|    | 3.2.2 Electromagnetic Calorimetry: ECAL and Preshower                    |    |

|    | 3.2.3 Hadronic Calorimetry: HCAL                                         |    |

|    | 3.2.4 Muon System                                                        |    |

|    | 3.2.5 Magnet System                                                      |    |

|    | 3.3 A TOROIDAL LHC APARATUS (ATLAS)                                      |    |

|    | 3.3.1 Inner Detector                                                     |    |

|    | 3.3.2 Calorimetry                                                        |    |

|    | <ul><li>3.3.2.1 Liquid Argon Calorimeter</li></ul>                       |    |

|    | 3.3.2.2       Tile Calorimeter (TileCal)         3.3.3       Muon System |    |

|    | 3.3.4 Magnet System                                                      |    |

| 4  | 4.1 SILICON DETECTOR MODULES DESCRIPTION                                 |    |

|    | 4.2 READ-OUT ELECTRONICS                                                 |    |

|    | 4.3 ROD DESCRIPTION                                                      |    |

|    | 4.4 MOTIVATION                                                           |    |

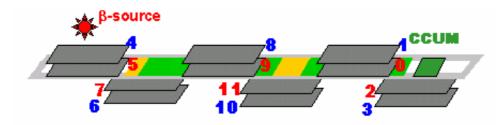

| 5  | 5 SYSTEM TEST SETUP                                                      |    |

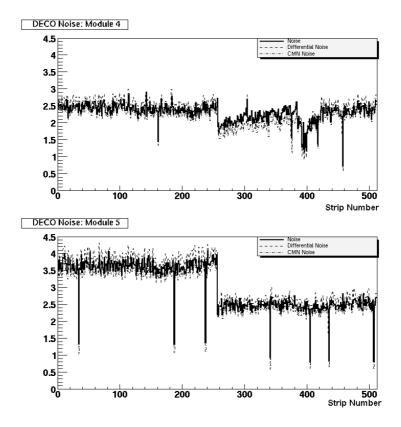

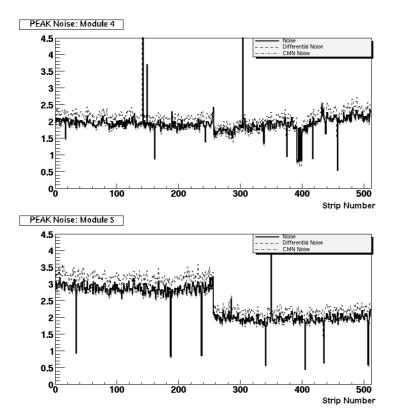

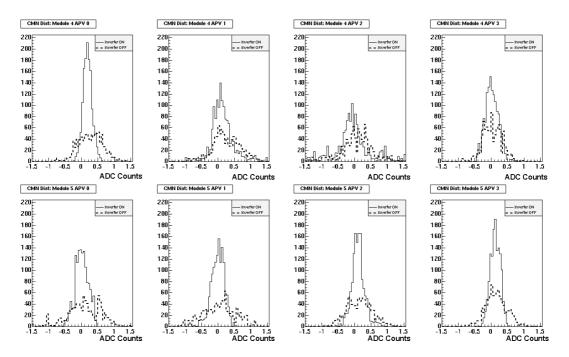

| 6  | 5 NOISE ANALYSIS                                                         | 43 |

|    | 6.1 DEFINITIONS                                                          |    |

|    | 6.2 Results                                                              |    |

|    | 6.2.1 Pedestals                                                          |    |

|    | 6.2.2 Noise                                                              |    |

|    | 6.2.3 Common Mode Noise                                                  |    |

|    | 6.3 BAD STRIPS DEFINITION                                                |    |

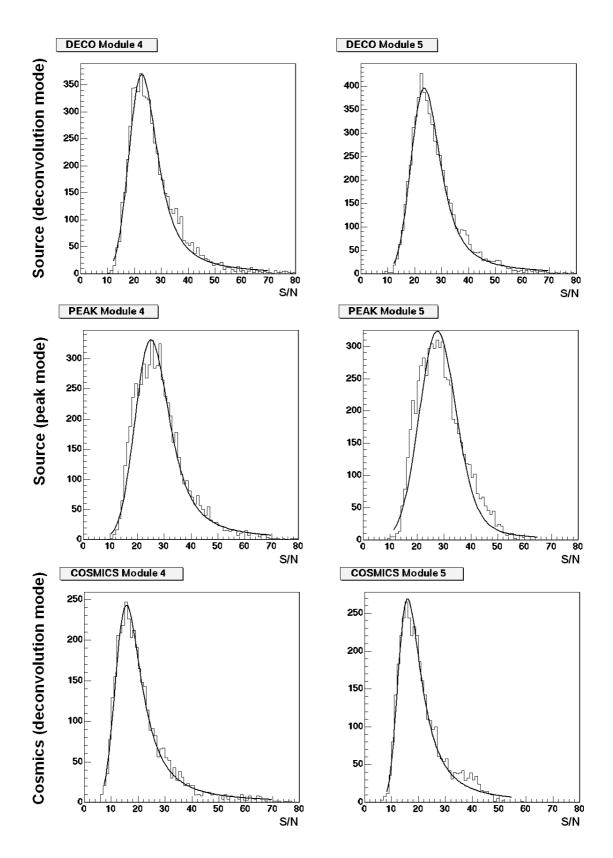

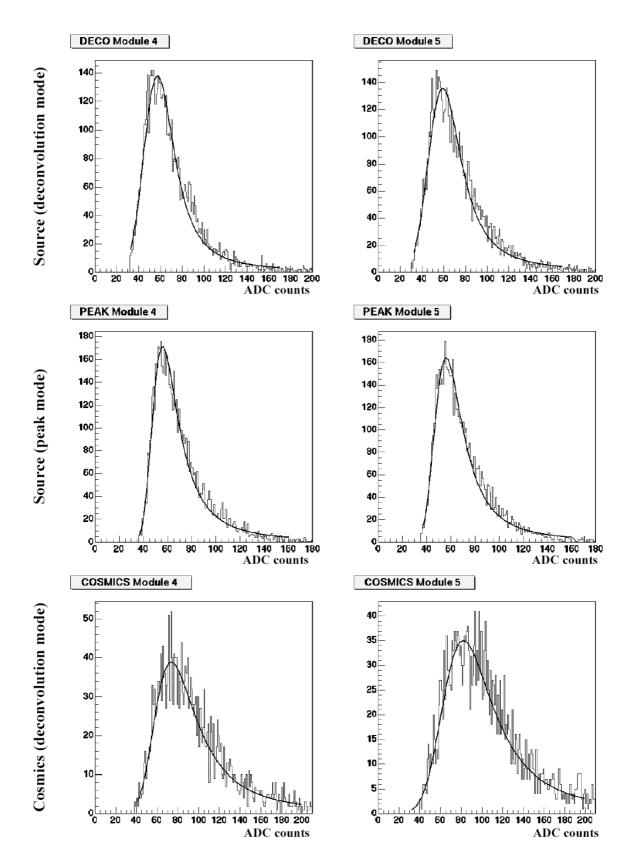

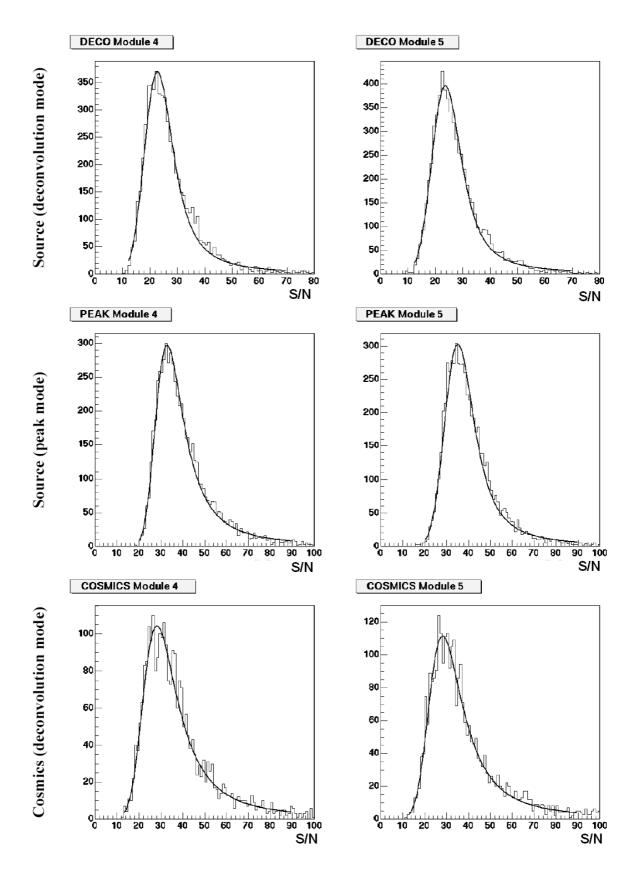

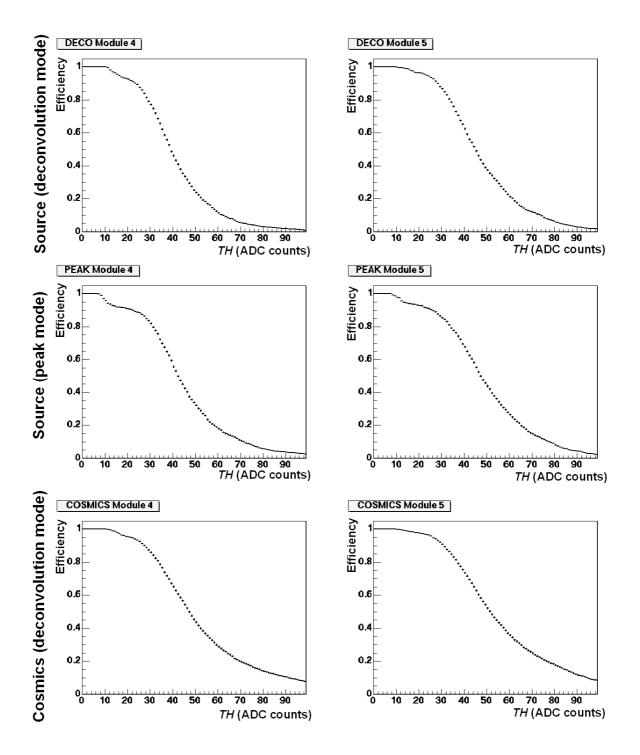

| 7  | 7 SIGNAL ANALYSIS                                                        | 48 |

|    | 7.1 Cluster Algorithms and Cluster Thresholds                            |    |

|    | 7.2 Results                                                              |    |

|    | 7.2.1 Gaussian-Landau Convolution Fit                                    |    |

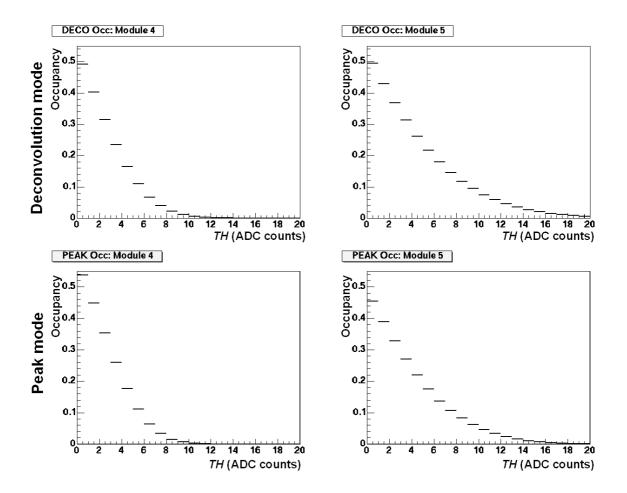

| 8  | 8 NOISE OCCUPANCY                                                        | 57 |

|    | 8.1 DEFINITION                                                           | 57 |

|    | 8.2 RESULTS                                                              |    |

| 0  |                                                                          |    |

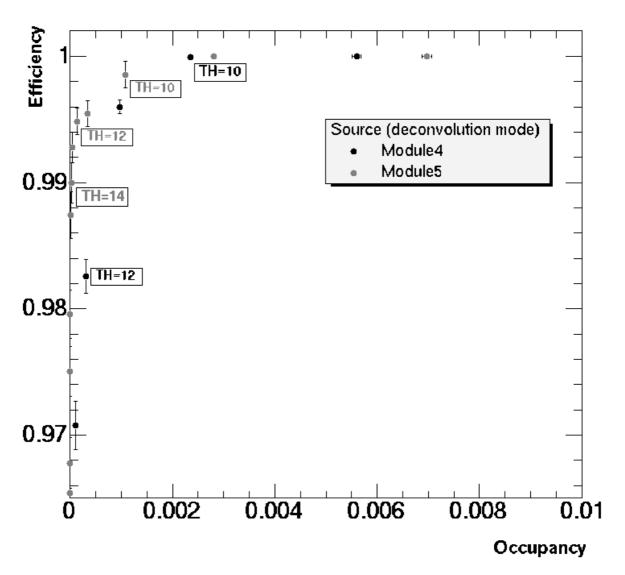

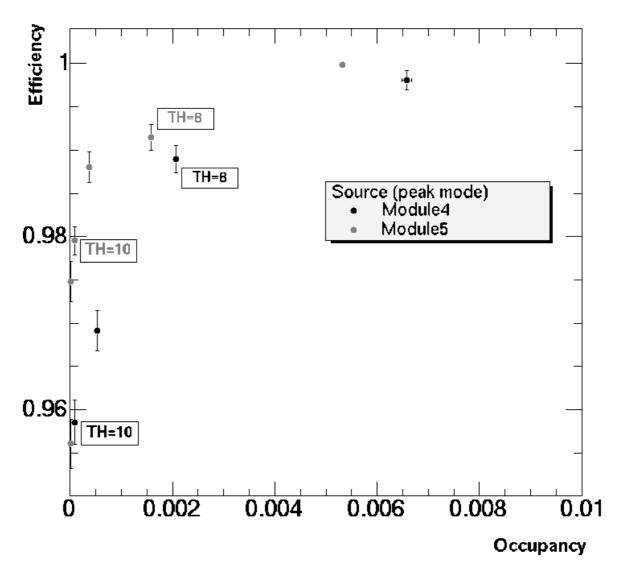

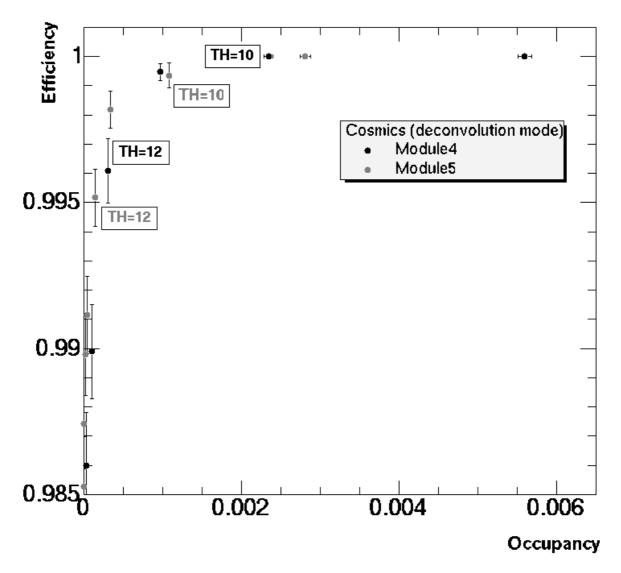

| 9  | SIGNAL EFFICIENCI                                                        |    |

| REFE | REFERENCES ON PART 1                 |   |  |

|------|--------------------------------------|---|--|

| 10   | SIGNAL EFFICIENCY VS NOISE OCCUPANCY | 0 |  |

| 9.2  | RESULTS                              | 8 |  |

| 9.1  | DEFINITION                           | 7 |  |

###

| 11  | INTROD               | DUCTION                              | 68 |

|-----|----------------------|--------------------------------------|----|

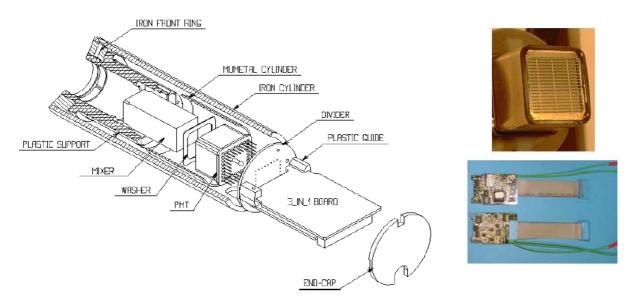

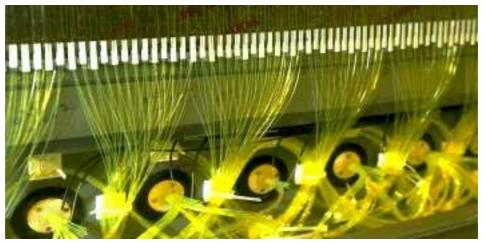

| 11. | 1 TILECA             | AL FRONT-END ELECTRONICS             |    |

|     | 11.1.1 Pl            | MT Block                             |    |

|     | 11.1.1.1             | Photomultipliers                     |    |

|     | 11.1.1.2             | Light Mixers                         |    |

|     | 11.1.1.3             | Magentic shielding                   |    |

|     | 11.1.1.4             | HV Dividers                          |    |

|     | 11.1.1.5             | 3-in-1 Boards                        |    |

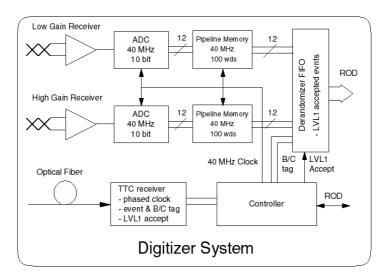

|     |                      | igitizer System                      |    |

|     |                      | igitizer-to-Slink Interface Links    |    |

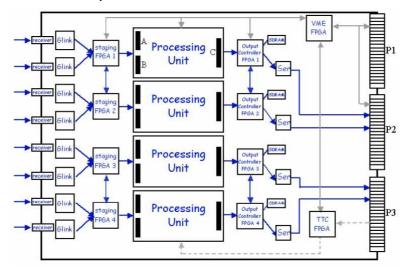

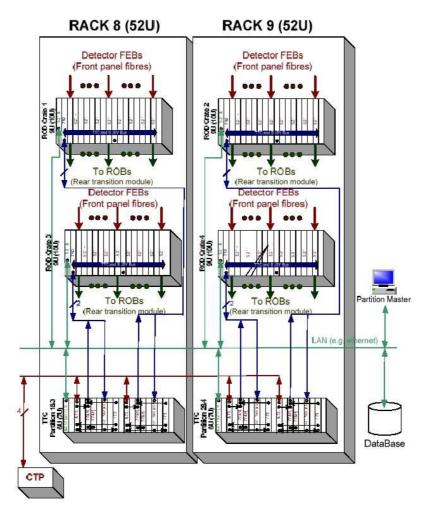

| 11. |                      | AL BACK-END ELECTRONICS: ROD CRATE   |    |

|     |                      | verview Set-up                       |    |

|     | 11.2.1.1             | Crate Controller                     |    |

|     | 11.2.1.2             | Trigger and Busy Module (TBM)        |    |

|     | 11.2.1.3             | ROD Motherboard                      |    |

|     | 11.2.1.4             | Transition Module                    |    |

|     |                      | OD Description                       |    |

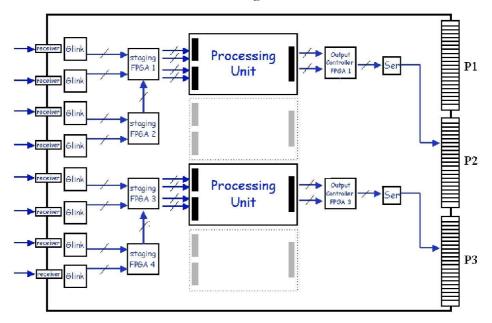

|     | 11.2.2.1             | Optical receivers and G-link chips   |    |

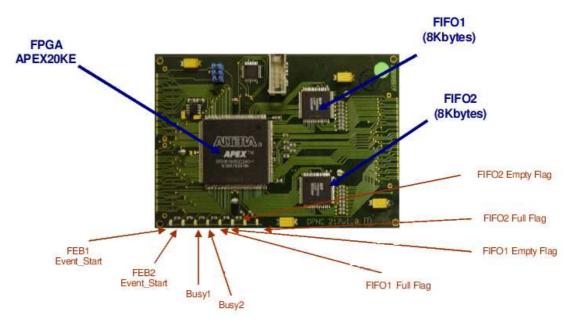

|     | 11.2.2.2             | Staging FPGAs                        |    |

|     | 11.2.2.3             | Output Controller FPGAs              |    |

|     | 11.2.2.4             | VME FPGA                             |    |

|     | 11.2.2.5             | TTC Controller FPGA                  |    |

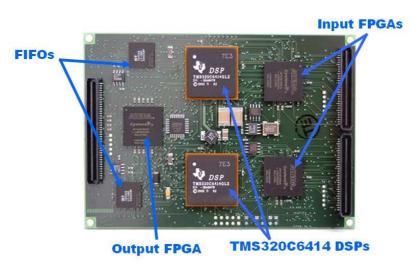

|     | 11.2.2.6             | Processing Units                     |    |

|     | 11.2.2.0<br>11.2.2.0 |                                      |    |

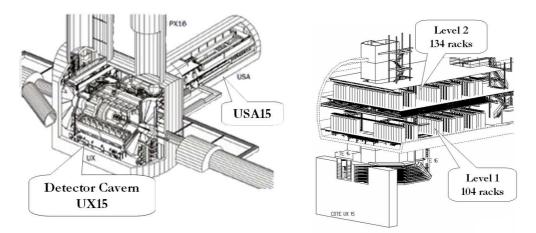

|     |                      | 6.2 DSP PU<br>Installation for ATLAS |    |

|     |                      | vstem Test Setups                    |    |

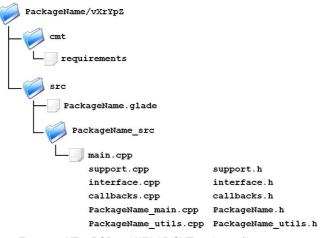

| 12  | -                    | ALONE SOFTWARE FOR ROD TESTS         |    |

|     |                      |                                      |    |

| 13  |                      | LATION AND SETUP                     |    |

| 14  |                      | ARE DEVELOPMENT                      |    |

| 15  |                      | KTESTROD                             |    |

| 15. |                      | MEBUS MENU                           |    |

| 15. |                      | ΓCVI MENU                            |    |

|     |                      | TCvi L1A Trigger                     |    |

|     |                      | unch Crossing and Orbit Register     |    |

|     |                      | vent/Orbit Counter Register          |    |

|     |                      | -Go Channels                         |    |

| 15. |                      | OD FINAL MENU                        |    |

|     |                      | ME Controller                        |    |

|     | 15.3.1.1             | Local Register                       |    |

|     | 15.3.1.2             | IRQ Registers                        |    |

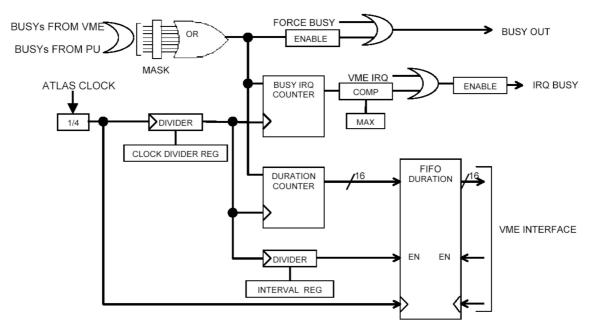

|     |                      | usy Registers                        |    |

|     | 15.3.2.1<br>15.3.2.2 | Miscellaneous Register               |    |

|     | 15.3.2.2             | Status Register<br>Timing counters   |    |

|     | 10.0.4.0             |                                      |    |

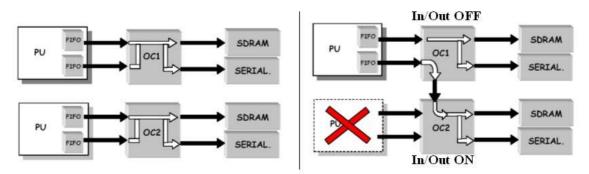

| 15.3.3   | Output Controller                          |     |

|----------|--------------------------------------------|-----|

| 15.3.3   | 6 6                                        |     |

| 15.3.3   | 6                                          |     |

| 15.3.3   |                                            |     |

| 15.3.3   | B.4 Dummy Register                         | 92  |

| 15.3.3   | 5.5 Version Register                       |     |

| 15.3.4   | TTC Controller FPGA                        |     |

| 15.3.4   | 1.1 Control Register                       |     |

| 15.3.4   | 2 Status Register                          | 93  |

| 15.3.4   |                                            |     |

| 15.3.4   |                                            |     |

| 15.3.5   | Staging FPGA                               |     |

| 15.3.5   |                                            |     |

| 15.3.5   |                                            |     |

| 15.3.5   | -                                          |     |

| 15.3.5   |                                            |     |

| 15.3.5   |                                            |     |

| 15.3.5   |                                            |     |

| 15.3.5   |                                            |     |

|          | FPGA PU                                    |     |

|          |                                            |     |

| 15.3.6   | 6                                          |     |

| 15.3.6   | 6 6                                        |     |

| 15.3.6   | , e                                        |     |

| 15.3.6   | 6                                          |     |

| 15.3.6   |                                            |     |

| 15.3.6   |                                            |     |

| 15.3.6   | 5 6                                        |     |

| 15.3.6   |                                            |     |

| 15.3.7   | DSP PU                                     |     |

| 15.3.7   |                                            |     |

| 15.3.7   | 1                                          |     |

| 15       | 3.7.2.1 HPI Register                       | 102 |

| 15       | 3.7.2.2 McBSP2 Serial Data Register        | 102 |

| 15       | 3.7.2.3 Control Register                   | 102 |

| 15       | 3.7.2.4 Status Register                    | 103 |

| 15       | 3.7.2.5 Dummy Register                     | 103 |

| 15       | 3.7.2.6 Version Register                   |     |

| 15.3.7   | 1.3 Input FPGA submenu                     |     |

| 15       | 3.7.3.1 Configuration/Status Register      |     |

| 15       | 3.7.3.2 Programming Register               | 104 |

|          | 3.7.3.3 Version Register                   |     |

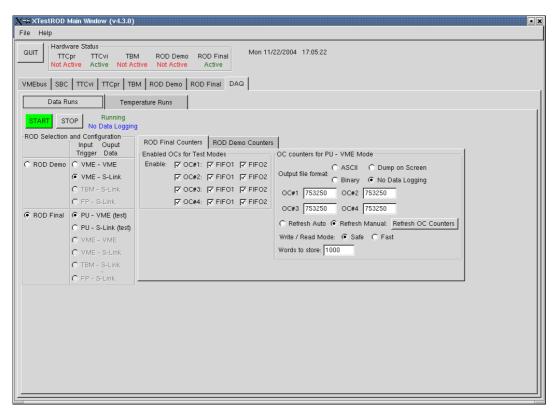

| 15.4 Thi | e DAQ Menu                                 |     |

| 15.4.1   | Data Runs submenu                          |     |

| 15.4.1   |                                            |     |

| 15.4.1   |                                            |     |

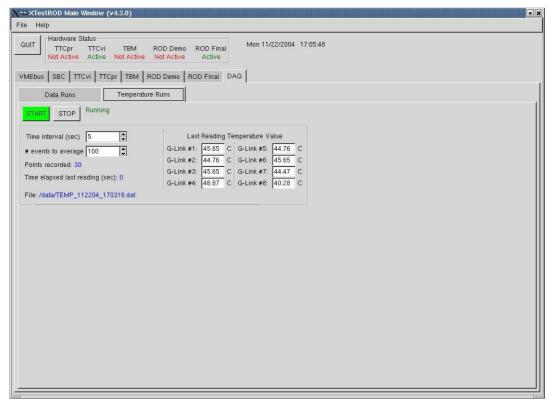

| 15.4.2   | Temperature Runs submenu                   |     |

|          | -                                          |     |

| 16 USIN  | G XFILAR                                   |     |

| 16.1 Thi | E FILAR MENU                               | 110 |

|          | e DAQ Menu                                 |     |

|          | -                                          |     |

| 17 XTES  | STROD AND XFILAR PERFORMANCE               | 110 |

| 17.1 RO  | DPRE-PRODUCTION TESTS                      | 111 |

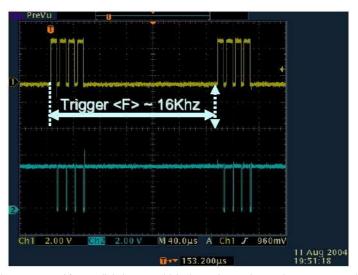

| 17.1.1   | Output Data Flow Tests                     |     |

| 17.1.1   |                                            |     |

| 17.1.1   |                                            |     |

| 17.1.1   | Full Input-Output Data Flow Tests          |     |

| 17.1.2   | · ·                                        |     |

| 17.1.2   |                                            |     |

|          |                                            |     |

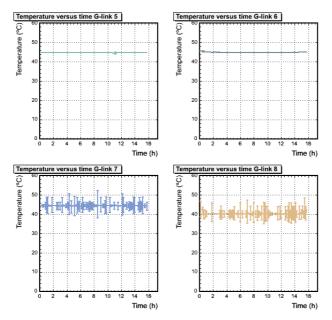

| 17.1.3   | ROD G-Link Temperature Tests at Laboratory | 110 |

| 17.1.4 Debug During ROD Firmware Development                                                                                                                                 |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

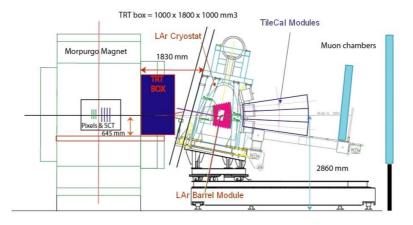

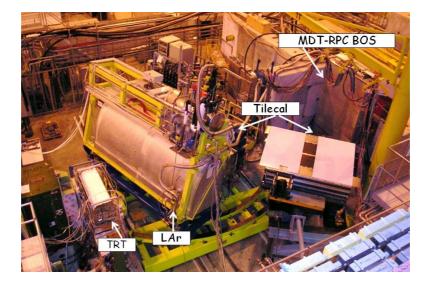

| 17.2 INTEGRATION AT THE COMBINED TEST BEAM SETUP                                                                                                                             |  |

| <ul> <li>17.1.4 Debug During ROD Firmware Development</li> <li>17.2 INTEGRATION AT THE COMBINED TEST BEAM SETUP</li> <li>17.3 PRE-ROD BOARD DEBUG AND DEVELOPMENT</li> </ul> |  |

| REFERENCES ON PART 2                                                                                                                                                         |  |

| CONCLUSIONS                                                                                                                                                                  |  |

| 18 CONCLUSIONS                                                                                                                                                               |  |

| APPENDIX I: ACRONYM LIST                                                                                                                                                     |  |

| APPENDIX II: FROM STANDARD MODEL PHYSICS TO LHC. A BRIEF                                                                                                                     |  |

| PHYSICS IN THE LAST YEARS AND THE NEAREST FUTURE                                                                                                                             |  |

| APPENDIX III: DEFINITION OF SOME PHYSICAL MAGNITUDES                                                                                                                         |  |

| ACKNOLEDGEMENTS                                                                                                                                                              |  |

# **Figures**

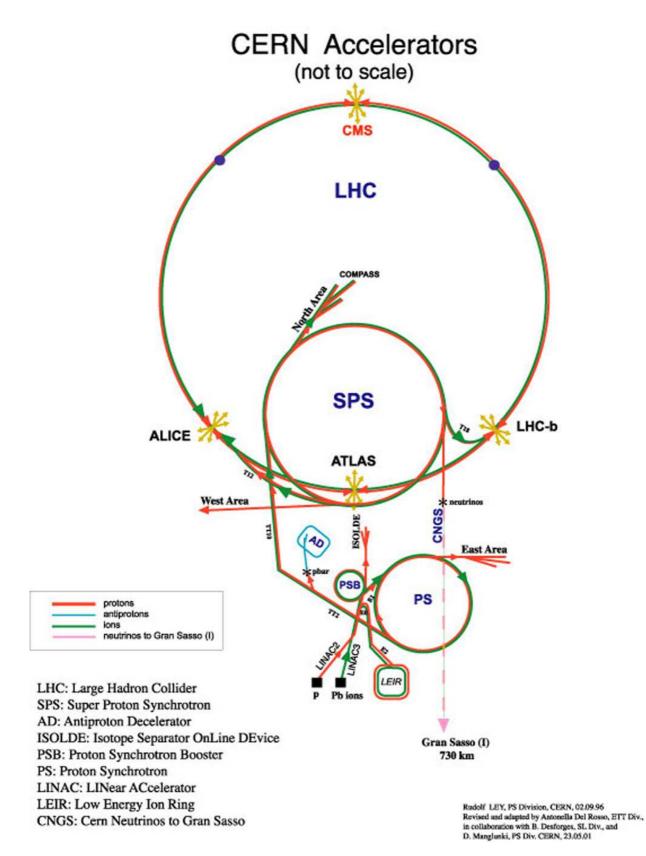

| FIGURE 1: SCHEME (NOT TO SCALE) OF THE CERN ACCELERATOR FACILITIES. NOTE THE BEAM LINES FOR ISOLDE A CNGS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

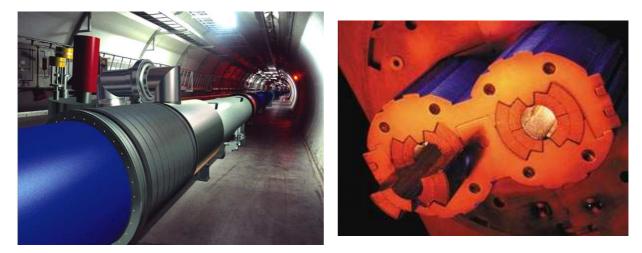

| FIGURE 2: ON THE LEFT, SIMULATION OF THE LHC IN THE TUNNEL. ON THE RIGHT, PICTURE OF THE DIPOLE MAGNET THE LHC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | FOR  |

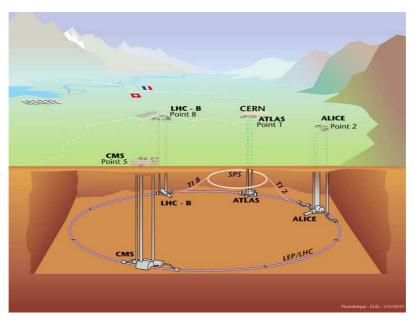

| FIGURE 3: SITUATION OF THE 4 EXPERIMENTS IN THE LHC IN THE ACCELERATOR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

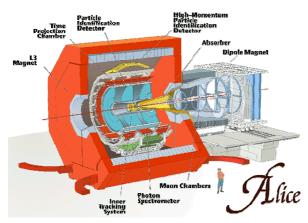

| FIGURE 4: DRAWING OF THE ALICE EXPERIMENT FOR THE LHC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

| FIGURE 5: SCHEME OF THE LHCB EXPERIMENT FOR THE LHC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

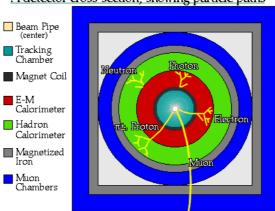

| FIGURE 6: SCHEME OF A TYPICAL PARTICLE DETECTOR (TRANSVERSE VIEW) FOR COLLIDING BEAM EXPERIMENTS. NO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| THE DIFFERENT PARTS AND THE BEHAVIOUR OF THE DIFFERENT TYPES OF PARTICLES INSIDE THE DETECTOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

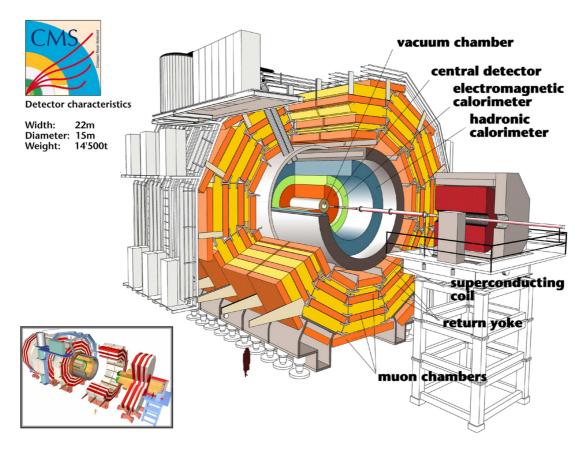

| FIGURE 7: THREE-DIMENSIONAL VIEW OF THE SUBDETECTORS IN CMS. NOTE THE ENDCAPS SHOWN IN THE LOWER LICORNER.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | EFT  |

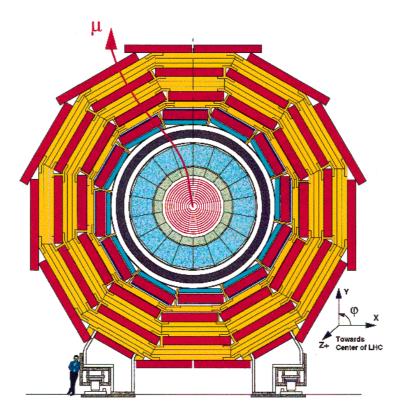

| FIGURE 8: AXIAL VIEW OF CMS. THE DIFFERENT SUBDETECTORS AND THE TRACK OF A MUON IN THE MAGNETIC FIEL ARE DISPLAYED.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | D    |

| FIGURE 9: DRAWING OF THE SILICON PIXEL DETECTOR, WHERE THE TWO LAYERS IN THE CENTRAL REGION AND THE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

| ENDCAP DISKS CAN BE SEEN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 26   |

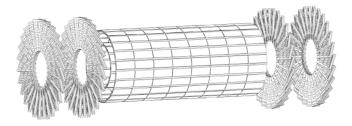

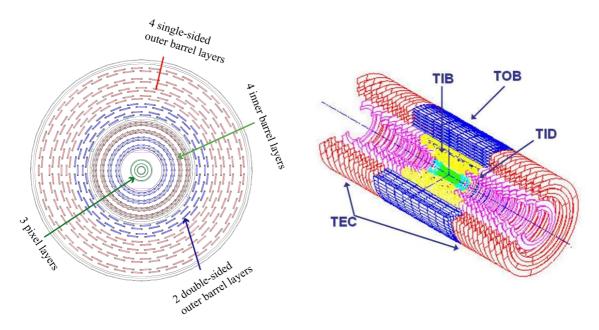

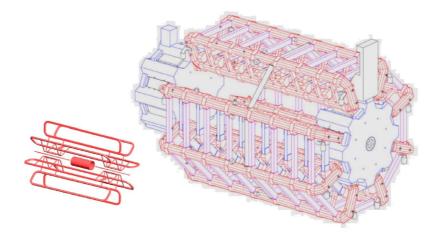

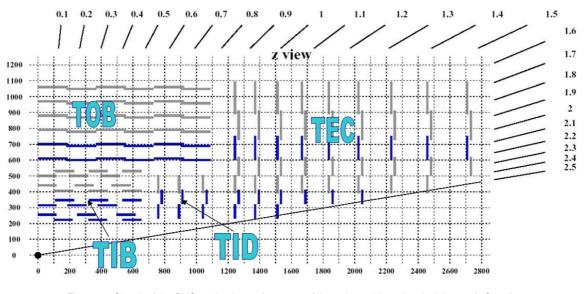

| FIGURE 10: ON THE LEFT, AXIAL VIEW OF THE DIFFERENT PARTS OF THE TRACKER SYSTEM IN THE BARREL REGION. C THE RIGHT, THREE-DIMENSIONAL LAYOUT OF THE CMS TRACKING DETECTORS, WHERE THE DIFFERENT PARTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| MENTIONED IN THE TEXT CAN BE OBSERVED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

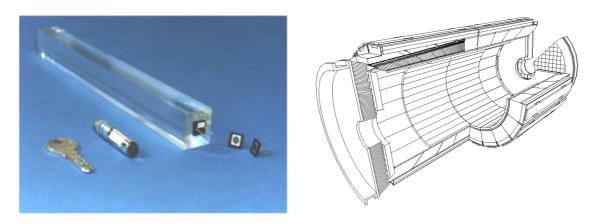

| FIGURE 11: ON THE LEFT, PICTURE OF ONE OF THE CRYSTALS TO BE USED IN THE ECAL BARREL WITH ITS PHOTODIOE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DES. |

| ON THE RIGHT, THREE-DIMENSIONAL VIEW OF THE ELECTROMAGNETIC CALORIMETER.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

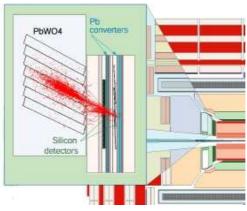

| FIGURE 12: SCHEMATIC VIEW OF AN EVENT IN THE PRESHOWER DETECTOR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

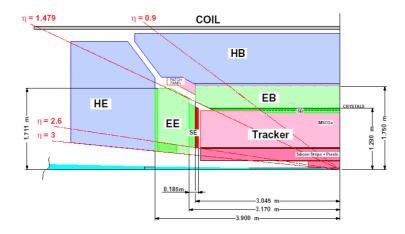

| FIGURE 13: SCHEMATIC VIEW OF ONE QUADRANT OF THE ELECTROMAGNETIC AND HADRONIC CALORIMETRY AND THE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ΙE   |

| TRACKING SYSTEM INSIDE THE SOLENOID COIL, WHERE THE DIFFERENT PARTS OF THE DETECTORS CAN BE SEEN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

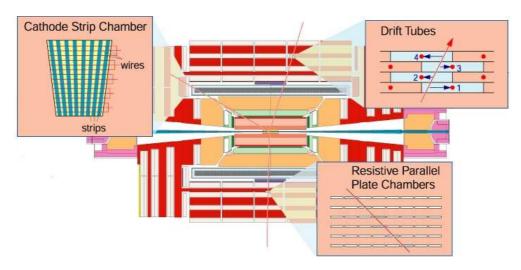

| FIGURE 14: SCHEMATIC VIEW OF THE DIFFERENT MUON DETECTORS AND THEIR EMPLACEMENT IN CMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

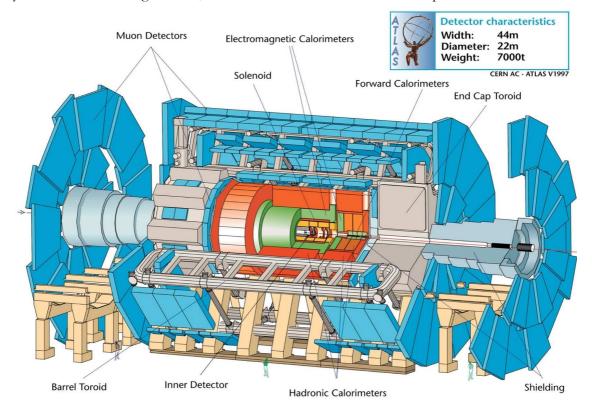

| FIGURE 15: THREE-DIMENSIONAL VIEW OF THE ATLAS DETECTOR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

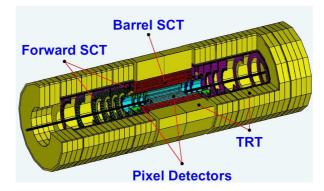

| FIGURE 16: THREE-DIMENSIONAL VIEW OF THE INNER DETECTOR WITH ALL THE SUBDETECTORS ARE LABELLED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

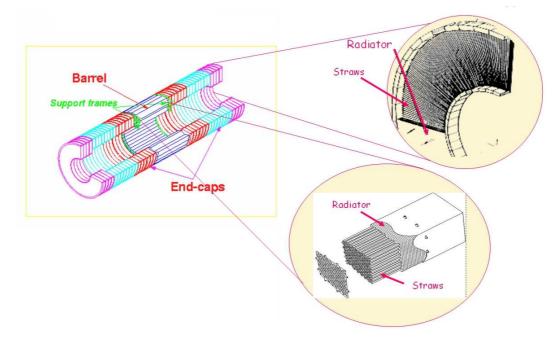

| FIGURE 17 : TRT BARREL AND ENDCAPS STRAWS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

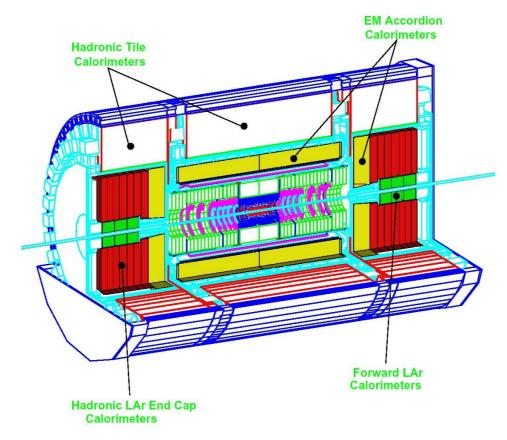

| FIGURE 18: SCHEME OF THE CALORIMETERS IN ATLAS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| FIGURE 19: THREE-DIMENSIONAL VIEW OF THE LAR CALORIMETERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

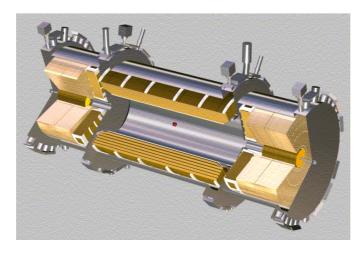

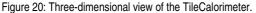

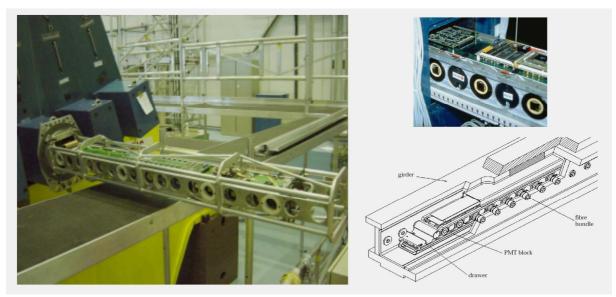

| FIGURE 20: THREE-DIMENSIONAL VIEW OF THE TILECALORIMETER.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

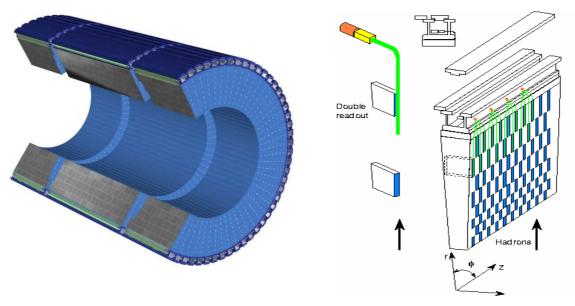

| FIGURE 21: PRINCIPLE OF THE TILECAL DESIGN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| FIGURE 22: LAYOUT OF THE CELLS OF THE TILECAL BARREL (LEFT) AND EXTENDED BARREL (RIGHT) MODULES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 35   |

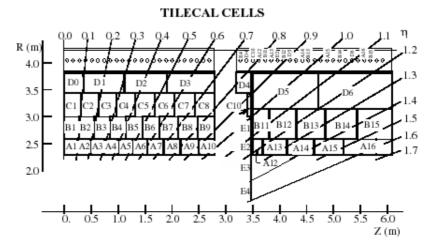

| FIGURE 23: THREE-DIMENSIONAL VIEW OF THE MUON SPECTROMETER INSTRUMENTATION INDICATING THE AREAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| COVERED BY THE FOUR DIFFERENT CHAMBER TECHNOLOGIES.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 36   |

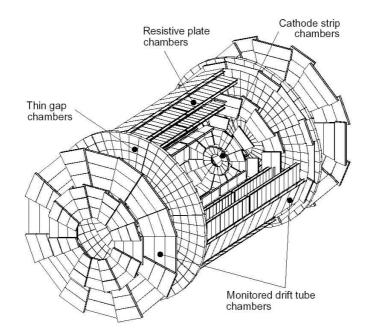

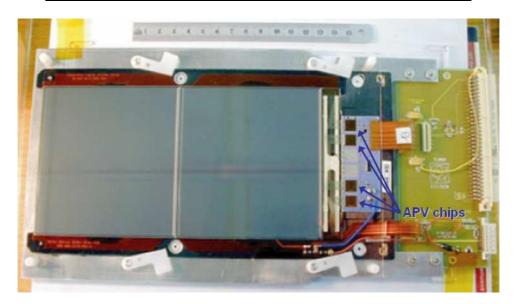

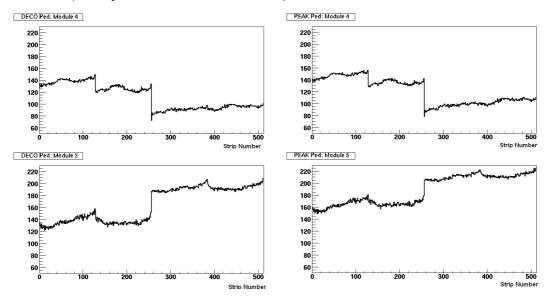

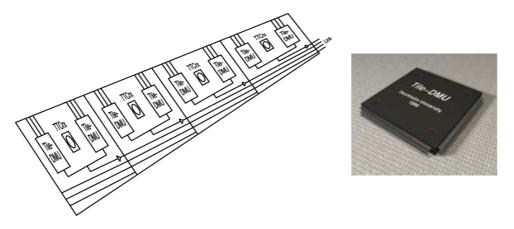

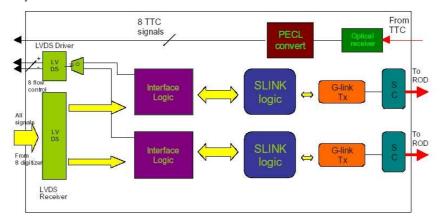

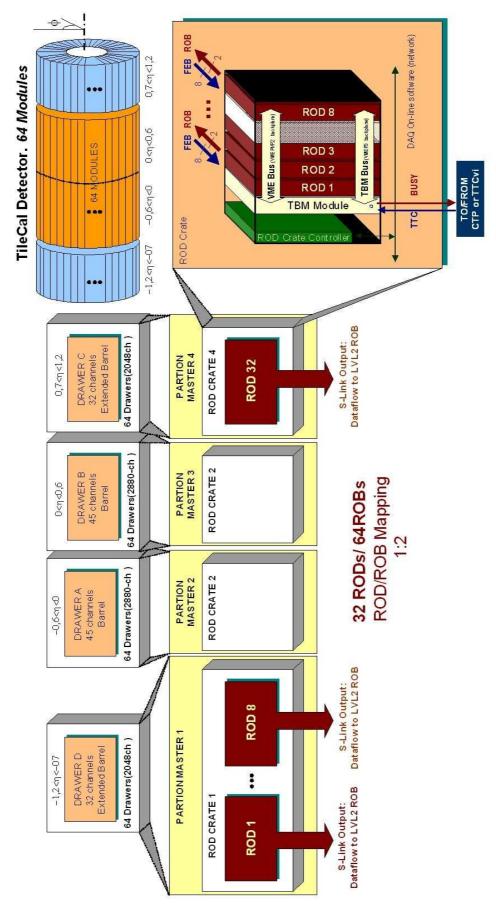

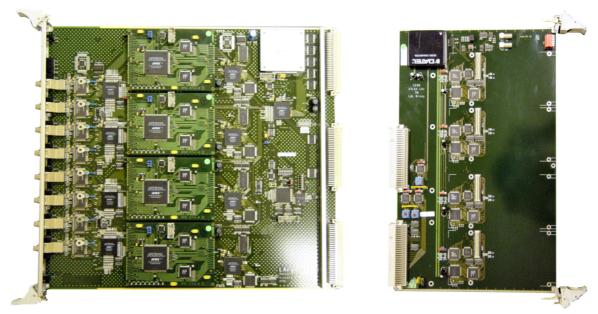

| FIGURE 24: TWO-DIMENSIONAL VIEW IN THE XY DIRECTION OF THE MUON SPECTROMETER SYSTEM. NOTE THE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |